Middle-East Journal of Scientific Research 24 (Techniques and Algorithms in Emerging Technologies): 373-379, 2016 ISSN 1990-9233; © IDOSI Publications, 2016 DOI: 10.5829/idosi.mejsr.2016.24.TAET23342

# VLSI Modelling of FM0 and Phase Encoding Using Balanced-Logic Operation with Pulse Generator for Adaptive Transportation

*R. Suresh, M. Anto Bennet, T.R. Dinesh Kumar, V. Sushmitha, R. Sarumathi and J. Sankari Gomathi*

Department of ECE, VELTECH, Chennai-600062, India

**Abstract:** The Dedicated Short-Range Communication (DSRC) is associate rising customary to push the conveyance communication into trendy automotive trade. The DSRC customary typically applies FM0 and Manchester to succeed in DC-balance enhancing the signal dependability. However, the intrinsic unbalance computation load between FM0 and Manchester makes their VLSI design with poor hardware utilization. The SOLS technique eliminates the limitation on hardware utilization by 2 core techniques: space compact retiming and balance logic-operation sharing. The paper additionally proposes concerning the heartbeat(pulse) generator circuit that is employed to reduce the delay, power consumption and it improves the potency of the system by increasing the number of knowledge sent over a amount of clock cycle. This project developed victimisation XILINX ten. Itools and model sim .

**Key words:** Dedicatedshort-range communication (DSRC) • FM0 • Manchester • Similarity adjusted logic simplification(SOLS)

# **INTRODUCTION**

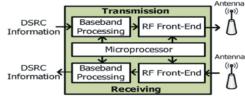

The dedicated short-range communication (DSRC) [1] could be a protocol for one- or two-way medium vary communication particularly for intelligent transportation systems as in Fig. 1. The DSRC will be in short classified into 2 categories: automobile-to-automobile and automobile-to-roadside [2]. In automobile-to-automobile, the DSRC allows the message causing and broadcasting among cars for questions of safety and public data announcement .the security problems embody blind-spot, intersection warning, lay cars distance and collision-alarm. The automobile-to-roadside focuses on the intelligent transportation service, like electronic toll assortment (ETC) system. With ETC, the toll aggregation is electrically accomplished with the contactless IC-card platform. Moreover, the ETC will be extended to the payment for parking-service and gas-refueling. Thus, the DSRC system plays a vital role in trendy industry. The system design of DSRC transceiver [3] is shown in Fig. 1. The higher and bottom components are dedicated for transmission and receiving, severally. This transceiver is assessed into 3 basic modules: micro chip, baseband process and RF front-end [4]. The micro chip interprets

directions from media access management to schedule the tasks of baseband process and RF front-end. The baseband process is chargeable for modulation, error correction, clock synchronization and coding. The RF frontend transmits and receives the wireless signal through the antenna.

Fig. 1: DRSC Tranceiver

# Ease of Use

**FM0 Encoding:** FM0 encoding writing [1] is additionally referred to as as bi-phase house secret writing theme. In FM0 encoding [1], [2], the signal to be transmitted and done in line with the subsequent rules,

- It inverts the section of the bottom band signal at the boundary of every image.

- For representing logic '0' level, it inverts the signal at the middle of the image.

• For representing logic'1'level, it constant voltage occupying a complete bit window.

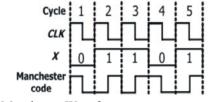

A FM0 coding [1] [2] [3] example is shown in Fig. 2. At cycle 1, the X is logic-0; thus, a transition happens on its FM0 code [5], in line with rule one. For simplicity, this transition is at the start set from logic-0 to -1. in line with rule three, a transition is allotted among every FM0 code and thereby the logic-1 is modified to logic-0 within the starting of cycle a pair of.

Then, in line with rule a pair of, this logic-level is hold with none transition in entire cycle a pair of for the X of logic-1. Thus, the FM0 code of every cycle is derived with these 3 rules mentioned earlier.

Fig. 2: FM0 Encoding Waveform

**Manchester Encoding:** The Manchester coding [1] example is shown in Fig. 3. The Manchester code comes from,

X (XOR) CLK: The Manchester encoding [6] is accomplished with a XOR operation for CLK and X. The clock perpetually encompasses a transition at intervals one cycle, so will the Manchester code notwithstanding what the X is. Manchester code ensures frequent line voltage transitions, directly proportional to the clock rate; this helps clock recovery [7]. The DC element of the encoded signal and thus carries no information, permitting the signal to be sent handily by media (e.g., Ethernet) that typically don't convey a DC element.

Fig. 3: Manchester Waveform

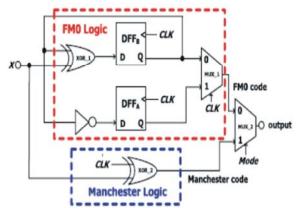

Architecture for FM0 and Manchester Encoding Techniques Using Sols Techniques: The literature [1] proposes a VLSI design of Manchester encoder for optical communications. This style adopts the CMOS electrical converter and therefore the gated electrical converter because the switch to construct Manchester encoding [6]. The literature [1] develops a high-speed VLSI design nearly totally reused with Manchester and Miller encodings for oftenness identification (RFID) applications [8]. This style is realised in zero.35-µm CMOS technology and therefore the most operation frequency is two hundred megacycle. The literature [5] proposes a Manchester coding design for UHF RFID tag individual. This hardware architecture [5] is conducted from the finite state machine (FSM) of Manchester code and is realised into field-programmable gate array (FPGA) prototyping system. the most operation frequency of this style is concerning 256 megacycle. The similar style methodology is any applied to one by one construct FM0 and Miller encoders conjointly for ultrahigh frequency RFID Tag individual. Its most operation frequency is concerning 192 megacycle. moreover, combines frequency shift keying (FSK) modulation and reception with Manchester code in hardware realization [3].

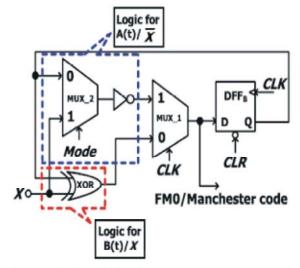

Fig. 4: FM0 and Manchester Encoding Techniques

The FM0 and MANCHESTER encoding [1, 5] techniques shown in Fig. 4 has some disadvantage. that's the output are anybody, either FM0 or MANCHESTER. To get the each secret writing output and to eliminated this disadvantage by reducing 2 flipflop into one flipflop and their circuit space was reduced.

The balanced and unbalanced circuit offers aintial stage of mode choice then the output square measure processed by mode choice and clock pulses. The balanced stage and unbalanced stage square measure outlined by their robust and week logic pulses [9]. The circuit of balanced and unbalanced square measure shown in Fig. 5 and Fig. 6.

Fig. 5: Balanced Circuit.

Fig. 6: Unbalanced Circuit

#### **Proposed Design**

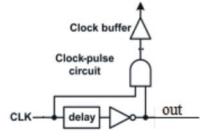

Pulse Triggered Flipfop for Minimization of Delay and Power Consumption: Pulse generators [9] is employed to get the oblong pulses and it should permit management over the increase time and fall time of the pulses. Pulse generators square measure on the market for generating output pulses having widths (duration) starting from minutes all the way down to below one time unit.Pulse generators square measure typically voltage sources, with true current pulse generators being on the market solely from a couple of suppliers.Pulse generators could use digital techniques, analog techniques, or a mix of each techniques to make the output pulses. for instance, the heart beat repetition rate and length is also digitally controlled however the heart beat amplitude and rise and fall times is also determined by analog electronic equipment within the output stage of the heart beat generator. With correct adjustment, pulse generators may also manufacture a five hundredth duty cycle sq. wave. Pulse generators square measure typically monophonic providing one frequency, delay, breadth and output.

Pulse generator circuit [9], contains shift registers and a buffer circuit. In register, it generate the periodic clock signals with reduced amplitude and rise and fall time of the clock signals. In buffer circuit, it will increase the driving capalitity and a knowledge storage.so these to enhance the planned circuit by generating the clock pulses with reduced ON TIME of the clock pulses. With these the heart beat generator is split into sub registers to generator next clock pulses with that reduced ON TIME, thus it consecutive generated in keeping with the heart beat clock signals given because the input to the pulse generator.

The output of the heart beat generator is given to the D-FF.Thus consequently supported the ontime of the periodic clock signals and therefore the ON TIME of the info signal, the output are going to be generated.

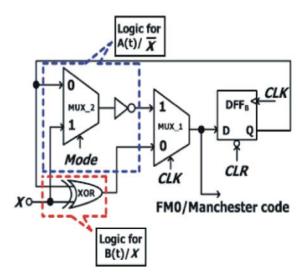

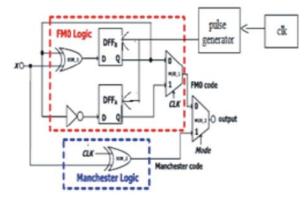

In the FMO AND MANCHESTER coding [10] as in circuit shown Fig. 7, the pulse generator is given to 2 D-FF because the input, so that the delay of the circuit is reduced to or so to s 7.02ns. In this, the output are going to be either FM0 or MANCHESTER depends on the mode choice at the last stage of electronic device.

Fig. 7: FM0 and Manchester Encoding Technique with Pulse Generator

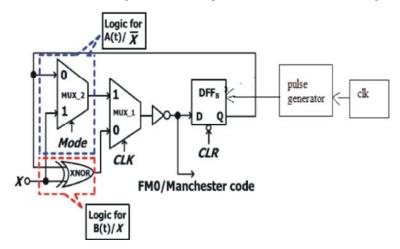

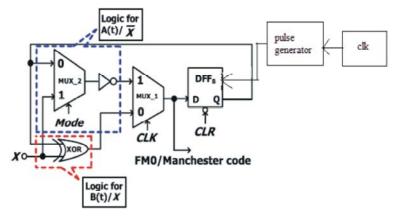

To get the each output of FM0 and MANCHESTER [11] this futhersplittedinto, the balanced and unbalanced circuit. This cacophonic relies on the robust and week signal of logic one and logic0. In this circuit, a 2 D-FF (Fig 7) is reduced to an single D-FF (Fig. 8 & Fig. 9) and a mode choice to chosen 1st with the assistance of electronic device, before process.

Middle-East J. Sci. Res., 24 (Techniques and Algorithms in Emerging Technologies): 373-379, 2016

| Table 1. Fertormance Comparison of Delay of Existing to Proposed System |                                                |                                                  |

|-------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------|

| FM0 and Manchester Technique Circuit(delay) (Fig.4)                     | Balanced Circuit (Fig. 5)                      | Inbalanced Circuit(fig. 6)                       |

| 8.625ns                                                                 | 7.000ns                                        | 7.027ns                                          |

| FM0 and Manchester Technique Circuit with Pulse                         |                                                |                                                  |

| Generator (Fig. 7)                                                      | Balanced Circuit with Pulse Generator (Fig. 8) | Unbalanced Circuit with Pulse Generator (Fig. 9) |

| 7.027ns                                                                 | 6.857ns                                        | 5.789ns                                          |

Table 1: Performance Comparison of Delay of Existing to Proposed System

Depends on the mode elect, the output are generated consecutive. In real time systems, initially a clock cycle is given and it operates at the same time. Thus it generates the output of each committal to writing consecutive.

Fig 8: FM0 and Manchester Encoding Balanced Circuit with Pulse Generator

Fig. 9: FM0 and Manchester Unbalanced Circuit with Pulse Generator

A Conventional Type of P-FF: A Conventional express sort P-FF [9]designs PF-FFs, in terms of pulse generation, is classified as associate implicit or a precise sort. In associate implicit sort P-FF, the heart beat generator is a component of the latch style and no express pulse signals are generated. In a precise sort P-FF, the heart beat generator and also the latch are separate .Without generating pulse signals expressly, implicit sort P-FFs are normally additional power-economical. However, they suffer from a extended discharging path, that results in inferior temporal arrangement characteristics. express

pulse generation, on the contrary, incurs additional power consumption however the logic separation from the latch style provides the FF style a novel speed advantage.

Pulse Generated Flipflops: The laborious -edged flipflops [9] area unit characterised by positive setup time inflicting giant D to Q delays.to cut back this disadvantage the heartbeat triggered flip-flops has been projected. It reduces the 2 stages into one stage and it's characterised by soft edge property. for prime speed operations of the standard master-slave flip-flop a preferred different is pulse triggered flip-flop. A pulse triggered flip-flop consists of generator for generating stroboscope signals and a latch for information storage. The logic complexness and range of stages within these pulse triggered flip-flop area unit reduced little D to delay. Pulse triggered flip-flop area unit classified into 2 sorts implicit pulse triggered flip-flop and specific pulse triggered flip-flop. In implicit pulse triggered flip-flop the heartbeat generated within the flip-flop. For example: information close to output, Hybrid latch flip-flop (HLFF) [9], semi dynamic flipflop. the heartbeat generation electronic equipment needs delicate pulsewidth management within the face of method variation and also the configuration of pulse clock distribution network. Depending on the strategy of pulse generation, P-FF styles may be classified as implicit or specific. implicit kind P-FF, the heartbeat generator may be a in-built logic of the latch style and no specific pulse signals area unit generated. In associate explicit-type P-FF [9], the styles of generator and latch area unit separate. Implicit pulse generation is usually thought of to be additional power economical than specific pulse generation. this is often as a result of the previous just controls the discharging path whereas the latter has to physically generate a pulse train. Implicit-type styles, however, face a prolonged discharging path in latch style, that ends up in inferior temporal arrangement characteristics. matters deteriorates more once low power techniques like conditional capture, conditional precharge, conditional discharge or conditional information mapping area unit applied.

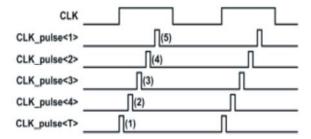

Fig. 10: Pulse Generator Waveform

Fig. 11: Block Diagram of Pulse Generator

**Pulse Generator Waveform:** A Waveform of Fig. 10 is shown in the Fig. 12. And the pulse generation of a single clock pulse is shown in Fig. 13.

Fig. 12: A Pulse Generated Clock Waveform

Fig. 13: A Generation of Single Clock Pulse Using Pulse Generator

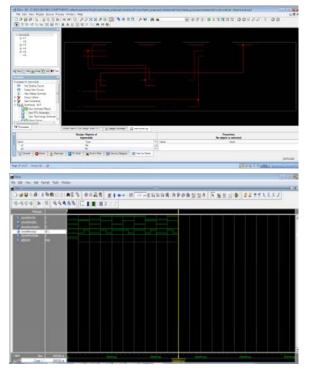

## Results and Performance Outcomes FMO Andmanchesterwith Pulse Generator:

Fig. 14a: A Pulse Generated Outputand Rtl Schematic of Fm0 and Manchester Coding of Fig. 7.

Balanced Circuit with Pulse Generator:

Fig. 14b: A Pulse Generated Output and Rtl Schematic of Balanced Circuit of Fig. 8

Unbalanced Circuit with Pulse Generator:

Fig. 14c: A Pulse Generated Output and Rtl Schematic of Unbalanced Circuit of Fig. 9

#### CONCLUSION

In this paper, proposes regarding the heart beat generator circuit that is employed to reduce the delay, power consumption and it improves the potency of the system by increasing the quantity of information sent over a amount of clock cycle. so the ultimate output offers a reduced delay in comparison to the exiting system. An economical approach of reducing delay is planned during this paper and power consumption is additionally analysed. The clock pulses offers an important role to reduced the delay and power consumption.

### REFERENCES

- 1. Yu- Hsuan Lee and Cheng-Wei Pan, 2015. "a fully reused VLSI architecture, "inproc. IEEE, 4(5).

- Efficient and high speed vlsimodelling of fm0/manchester encoding using sols technique and clock gating technique for dedicated short range communication applications IJSART - 1(6).

- Design and Implementation of DSRC Encoders for Efficient Hardware UtilizationInternational Journal of Innovative Research in Science, Engineering and Technology(An ISO 3297: 2007 Certified Organization), 4(7), July 2015.

- Kenney, J.B., 2011. "Dedicated short-range communications (DSRC) standards in the United States," Proc. IEEE, 99(7): 1162-1182.

- Power Reduction in the VLSI Architecture of FM0 and Manchester Encoding IJSRD -International Journal for Scientific Research & Development, 2(12), 2015 ISSN.

- Manchester Encoder and Decoder with Clock Recovery Unit and invalid detector Computer Engineering and Intelligent Systems ISSN 2222-1719 (Paper) ISSN 2222-2863 (Online) 6(2), 2015.

- A Review of Manchester, Miller and FM0 Encoding TechniquesSmart Computing Review, 4(6), December 2014.

- Reusable SOLS Encoder for DSRC Applications International Journal of Science a Research (IJSR) ISSN (Online): 2319-7064 Index Copernicus Value (2013): 6.14 |Impact Factor (2013): 4.438.

- 9. Low-power and area- efficient shift register using pulsed latch. IEEE Transaction on Circuits and System, 62(6).

Middle-East J. Sci. Res., 24 (Techniques and Algorithms in Emerging Technologies): 373-379, 2016

- Fully Reused VLSI Architecture of FM0/Manchester Encoding Technique for MemoryApplication International Journal of Science and Research (IJSR) ISSN (Online): 2319.Index Copernicus Value (2013): 6.14 | Impact Factor (2013): 4.438.

- Dattagupta, S., C.C. Lin and C.Y. Chan, 2012. "Basic safety message emulator using DSRC", 15<sup>TH</sup> International IEEE Annual Conference onIntelligent transportation system, Alaska 2012.